【電路知識】OC、OD門輸出、推挽輸出-KIA MOS管

信息來源:本站 日期:2022-11-09

集電極開路門(集電極開路 OC 或源極開路OD)

open-drain是漏極開路輸出的意思,相當(dāng)于集電極開路(open-collector)輸出,即ttl中的集電極開路(oc)輸出。一般用于線或、線與,也有的用于電流驅(qū)動。

open-drain是對mos管而言,open-collector是對雙極型管而言,在用法上沒什么區(qū)別。

開漏形式的電路有以下幾個特點(diǎn):

1.利用外部電路的驅(qū)動能力,減少IC內(nèi)部的驅(qū)動或驅(qū)動比芯片電源電壓高的負(fù)載。

2. 可以將多個開漏輸出的Pin,連接到一條線上通過一只上拉電阻,在不增加任何器件的情況下,形成“與邏輯”關(guān)系。這也是I2C,SMBus等總線判斷總線占用狀態(tài)的原理。

接容性負(fù)載時,下降延是芯片內(nèi)的晶體管,是有源驅(qū)動,速度較快;上升延是無源的外接電阻,速度慢。如果要求速度高電阻選擇要小,功耗會大。所以負(fù)載電阻的選擇要兼顧功耗和速度。

3.可以利用改變上拉電源的電壓,改變傳輸電平。例如加上上拉電阻就可以提供TTL/CMOS電平輸出等。

4.開漏Pin不連接外部的上拉電阻,則只能輸出低電平。一般來說,開漏是用來連接不同電平的器件,匹配電平用的。

5.正常的CMOS輸出級是上、下兩個管子,把上面的管子去掉就是OPEN-DRAIN了。這種輸出的主要目的有兩個:電平轉(zhuǎn)換和線與。

6.由于漏級開路,所以后級電路必須接一上拉電阻,上拉電阻的電源電壓就可以決定輸出電平。這樣就可以進(jìn)行任意電平的轉(zhuǎn)換了。

7.線與功能主要用于有多個電路對同一信號進(jìn)行拉低操作的場合,如果本電路不想拉低,就輸出高電平,因?yàn)镺PEN-DRAIN上面的管子被拿掉,高電平是靠外接的上拉電阻實(shí)現(xiàn)的。(而正常的CMOS輸出級,如果出現(xiàn)一個輸出為高另外一個為低時,等于電源短路。)

8.OPEN-DRAIN提供了靈活的輸出方式,但是也有其弱點(diǎn),就是帶來上升沿的延時。因?yàn)樯仙厥峭ㄟ^外接上拉無源電阻對負(fù)載充電,所以當(dāng)電阻選擇小時延時就小,但功耗大;反之延時大功耗小。所以如果對延時有要求,則建議用下降沿輸出。

在一個結(jié)點(diǎn)(線)上, 連接一個上拉電阻到電源 VCC 或 VDD 和 n 個 NPN 或 NMOS 晶體管的集電極 C 或漏極 D, 這些晶體管的發(fā)射極 E 或源極 S 都接到地線上, 只要有一個晶體管飽和, 這個結(jié)點(diǎn)(線)就被拉到地線電平上。

因?yàn)檫@些晶體管的基極注入電流(NPN)或柵極加上高電平(NMOS), 晶體管就會飽和, 所以這些基極或柵極對這個結(jié)點(diǎn)(線)的關(guān)系是或非 NOR 邏輯. 如果這個結(jié)點(diǎn)后面加一個反相器, 就是或 OR 邏輯。

注:個人理解:線與,接上拉電阻至電源。(~A)&(~B)=~(A+B),由公式較容易理解線與此概念的由來;

如果用下拉電阻和 PNP 或 PMOS 管就可以構(gòu)成與非 NAND 邏輯, 或用負(fù)邏輯關(guān)系轉(zhuǎn)換與/或邏輯。

注:線或,接下拉電阻至地。(~A)+(~B)=~(AB);

這些晶體管常常是一些邏輯電路的集電極開路 OC 或源極開路 OD 輸出端. 這種邏輯通常稱為線與/線或邏輯, 當(dāng)你看到一些芯片的 OC 或 OD 輸出端連在一起, 而有一個上拉電阻時, 這就是線或/線與了, 但有時上拉電阻做在芯片的輸入端內(nèi)。

順便提示如果不是OC或OD芯片的輸出端是不可以連在一起的, 總線 BUS 上的雙向輸出端連在一起是有管理的, 同時只能有一個作輸出, 而其他是高阻態(tài)只能輸入。

一般是指兩個三極管分別受兩互補(bǔ)信號的控制,總是在一個三極管導(dǎo)通的時候另一個截止,要實(shí)現(xiàn)線與需要用OC(open collector)門電路。如果輸出級的有兩個三極管,始終處于一個導(dǎo)通、一個截止的狀態(tài),也就是兩個三級管推挽相連,這樣的電路結(jié)構(gòu)稱為推拉式電路或圖騰柱(Totem- pole)輸出電路。

當(dāng)輸出低電平時,也就是下級負(fù)載門輸入低電平時,輸出端的電流將是下級門灌入;當(dāng)輸出高電平時,也就是下級負(fù)載門輸入高電平時,輸出端的電流將是下級門從本級電源拉出。

這樣一來,輸出高低電平時將交替工作,從而減低了功耗,提高了每個管的承受能力。又由于不論走哪一路,管子導(dǎo)通電阻都很小,使RC常數(shù)很小造成延時短,轉(zhuǎn)變速度很快。因此,推拉式輸出級既提高電路的負(fù)載能力,又提高開關(guān)速度。

推挽電路是兩個參數(shù)相同的三極管或MOSFET,以推挽方式存在于電路中,各負(fù)責(zé)正負(fù)半周的波形放大任務(wù),電路工作時,兩只對稱的功率開關(guān)管每次只有一個導(dǎo)通,所以導(dǎo)通損耗小效率高。

輸出既可以向負(fù)載灌電流,也可以從負(fù)載抽取電流。由于驅(qū)動能力大,所以多個推挽輸出不能并聯(lián)在一起這是與OC或OC門之間的不同點(diǎn)。

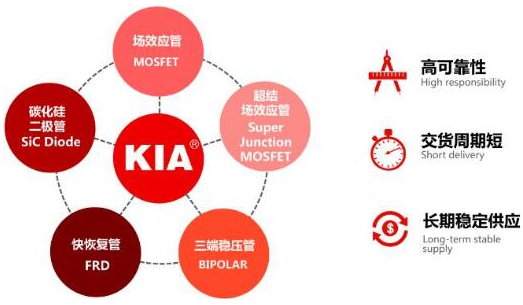

KIA半導(dǎo)體是一家致力于功率半導(dǎo)體電子元器件研發(fā)與銷售的高新技術(shù)型企業(yè),竭誠服務(wù)全球開關(guān)電源、綠色照明、電機(jī)驅(qū)動、汽車電子、新能源充電樁、太陽能設(shè)備、數(shù)碼家電、安防工程等行業(yè)長期合作伙伴,主動了解客戶需求,不斷研發(fā)創(chuàng)新,為客戶提供綠色、節(jié)能、高效的功率半導(dǎo)體產(chǎn)品。

聯(lián)系方式:鄒先生

聯(lián)系電話:0755-83888366-8022

手機(jī):18123972950

QQ:2880195519

聯(lián)系地址:深圳市福田區(qū)車公廟天安數(shù)碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導(dǎo)體”或掃一掃下圖“關(guān)注”官方微信公眾號

請“關(guān)注”官方微信公眾號:提供 MOS管 技術(shù)幫助

免責(zé)聲明:本網(wǎng)站部分文章或圖片來源其它出處,如有侵權(quán),請聯(lián)系刪除。