負載寄生電容對MOS管輸出波形的影響-KIAMOS管

信息來源:本站 日期:2022-04-06

調試一個模擬電路時,發現MOS管的輸出波形的上升沿和下降沿總是出現不對稱的情況,且兩者的斜率相差較大。通過仔細分析,發現問題出在負載的寄生電容上,也就是說負載的寄生電容會影響MOS管的充放電時間,進而導致MOS管輸出波形出現不對稱的情況。

現結合實際的測試情況,對MOS管輸出波形受負載寄生電容的影響做一下簡單的分析。

一、NMOS驅動負載

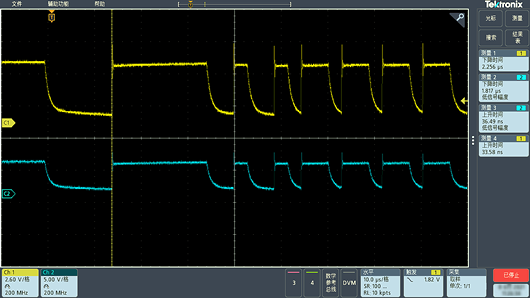

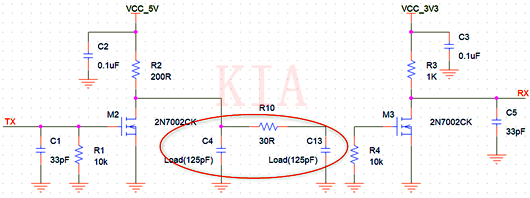

上圖是一個簡單的NMOS驅動負載的電路圖,其中,紅框中是一個帶有250pF寄生電容的負載。在斷開反饋回路的情況下,測得的負載上的波形如下圖所示。

波形1為負載之前的波形,波形2為負載之后的波形。斷開反饋回路。

NMOS管輸出波形受負載寄生電容的影響分析

N管柵極上升沿時,漏極處于下降沿狀態,下降沿時間約為N管柵極的寄生電容(輸入寄生電容和米勒電容)充電時間常數,由于未接限流電阻,所以,充電常數較小,即漏極的下降沿較短,實測只有13ns;

N管柵極下降沿時,漏極處于上升沿狀態,上升沿時間約為5V對模擬開關寄生電容的充電時間,充電電阻200Ohm,負載電容250pF(Type),對應充電常數50ns,實測波形上升沿為103ns;

二、NMOS+PMOS驅動負載

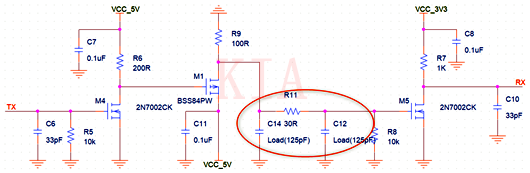

上圖是一個簡單的NMOS+PMOS驅動負載的電路圖,其中,紅框中是一個帶有250pF寄生電容的負載。在斷開反饋回路的情況下,測得的負載上的波形如下圖所示。

NMOS+PMOS輸出波形受負載寄生電容的影響分析

結合第一種情況的分析,N管柵極上升沿時,漏極處于下降沿狀態,下降沿時間較短,所以,P管柵極的下降沿時間也很短,進而P管漏極的上升沿也很短,實測只有15ns,跟第一種情況相當;

同樣,結合第一種情況的分析,N管柵極下降沿時,漏極處于上升沿狀態,5V電源開始給P管柵極寄生電容充電,即P管柵極處于上升沿,P管柵極上升沿時間約為5V對P管柵極寄生電容的充電時間,充電電阻為200Ohm,寄生電容約為73pF(Type),充電時間約為15ns;

此階段,P管漏極則處于下降沿,負載寄生電容250pF開始經P管的漏極電阻100Ohm放電,放電時間常數為25ns。這個過程是P管柵極充電使P管關斷導致負載寄生電容放電,是一個相互的作用,不過可以簡單計算為15ns+25ns=40ns。實測值為92ns。

上面的計算基本與實測值相差2倍,因為MOS管的寄生電容充放電是一個動態過程,不是簡單的乘積,考慮到這個因素,可以將計算結果乘2,即和實測相當。

三、總結

總的來講,如果只使用了N管的電路形式,則要考慮N管的漏極電阻阻值,如果阻值太大,會影響波形的上升沿,導致上升沿斜率太大;如果阻值太小則要考慮N管的導通電流和漏極電阻的功率問題。

如果使用了N管+P管的電路形式,則要同時考慮N管和P管的漏極電阻阻值,阻值太大,會使波形的下降沿變緩,阻值太小則要兼顧MOS的導通電路和電阻的功率問題。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助

免責聲明:本網站部分文章或圖片來源其它出處,如有侵權,請聯系刪除。