?電路設計中dummy的作用、MOS管的dummy解析-KIA MOS管

信息來源:本站 日期:2021-09-28

在IC版圖設計中除了要體現電路的邏輯或功能確保LVS驗證正確外,還要增加一些與LVS(電路匹配)無關的圖形,以減小中間過程中的偏差,我們通常稱這些圖形為dummy layer。

dummy layer的用途:

1、保證可制造性,防止芯片在制造過程中由于曝光過渡或不足而導致的蝕刻失敗:如在tapeout的時候會檢查芯片的density,插入dummy metal、dummy poly、dummy diff等;

2、避免由于光刻過程中光的反射與衍射而影響到關鍵元器件物理圖形的精度進又而影響其size:如在模擬電路的電阻、電容陣列外圍加上dummy res和dummy cap等,以及關鍵MOS附近加dummy MOS等;

3、避免芯片中的noise對關鍵信號的影響,在關鍵信號的周圍加上dummy routing layer后者dummy元器件:

如對于某些易受干擾的信號線除了盡量減小其走線長度外,還應該在其走線的左右和上下都加上dummy metal/poly并接地,保證其不受noise的影響。在cap外圍加dummy cap也有類似的作用。

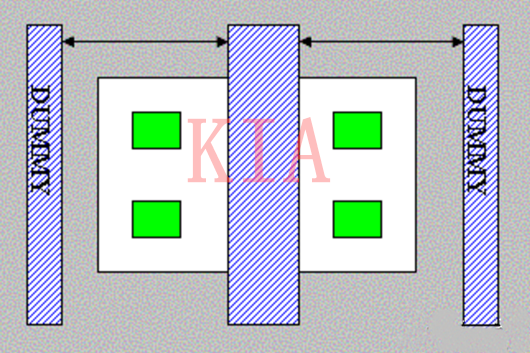

1、MOS dummy

在MOS兩側增加dummy poly,避免Length受到影響。對NMOS先加P type guard ring 連接VSS,接著加N type guard ring 連接VDD。

對PMOS先加N type 連接VDD,接著加P type連接VSS。拆分MOS應為偶數根,Source端與四周guar ring就近連接。比如拆分NMOS為偶數根, 連接VSS的端在外側并直接與四周guard ring相連。

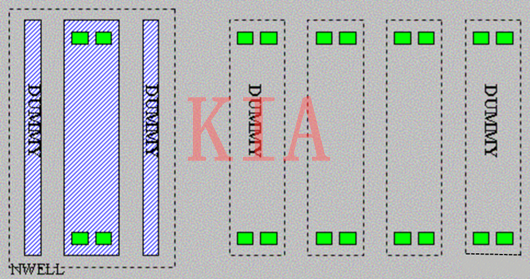

2、RES dummy

類似于MOS dummy方法增加dummy, 有時會在四周都加上。在poly/diff 電阻下面增加nwell 減輕noise 對電阻的影響,nwell連接高電位與sub反偏。

Nwell電阻四周加sub cont 連接VSS。Nwell電阻為了降低光照使電阻阻值下降的影響,在上面覆蓋metal并連接高電位。其次為給nwell電阻足夠的margin 通常nwell寬度5-6um。

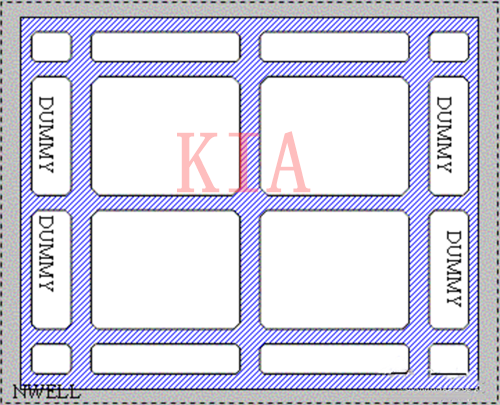

3、CAP dummy

增加dummy方法類似,用Nwell阻擋相自于substrate的noise,Nwell接高電位與sub 反偏。

4、關鍵走線與左右或上下走線的屏蔽采用相同層或中間層連接VSS來處理。

在MOS管的兩側增加Dummy POly,避免柵的長度受到影響,如下圖所示。

ADR510ART-R2當要加保護環時,對NMOS管先加P型保護環連接到地,接著加N型保護環連接到電源。對PMOS先加N型保護環連接到電源,接著加P型保護環連接到地。

類似于MOs的Dummy方法,有時會在四周都增加Dummy。在多晶或擴散區電阻的下面增加N阱可以減輕噪聲對電阻的影響,N阱連接高電位與襯底反偏,如圖所示。

為了降低光照使電阻阻值下降的影響,應在N阱電阻上面覆蓋金屬并連接高電位。

電容增加Dummy方法與MOs管類似,N阱用于阻擋來自襯底的噪聲,N阱接高電位,而襯底則反偏,如圖所示。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助