CMOS集成電壓比較器設計分析-KIA MOS管

信息來源:本站 日期:2021-06-28

電壓比較器是對輸入信號進行鑒幅與比較的電路,其功能是比較一個模擬信號和另一個模擬信號(參考信號),并以輸出比較得到的二進制信號。其在A/D轉換器、數據傳輸器、切換功率調節器等設備中有著廣泛的應用。

在高速度、高精度A/D轉換器中,比較器的精度和速度直接影響轉換電路的轉換精度和轉換速度等關鍵指標;在數據傳輸器中,比較器的性能對數據傳輸的誤碼率有著很大的影響;在切換功率調節器中,調節器的功率調節性能在很大程度上依賴于電壓比較器的性能。

因此,是高工作頻率、高增益、低失調電壓、高性能的電壓比較器,在模擬集成電路和數/模混合集成電路中十分重要。仿真結果表明,該電壓比較器適用于高速A/D轉換器、高速數據傳輸器及高性能切換功率調節器等設備中。

1.比較器電路設計

這里介紹的電壓比較器是傳統的預放大鎖存比較器,采用預放大器、鎖存比較器和輸出緩沖級級聯的方式來實現,其原理框圖如圖1所示。

如圖2中第一部分所示,M20和M21構成差分放大管;M4,M6組成有源負載。M2,M3分別與M4,M6并聯,以向差分放大管注人大電流,同時也減小了M4和M6的寬長比,降低了電路的輸入電容,以利于電路提高頻率特性。

該放大器的增益可表示為:

從式(1)可以看出,在管子寬長比確定后,Av與(1+ISD2/ISD4)1/2成正比,若M2向M21注入大電流,則在保證高頻時能提高放大器的增益。該放大器的增益為12.9 dB(4.415 7倍),3 dB帶寬為582.64 MHz。

(1)鎖存比較電路

鎖存比較電路是整個比較器的核心部分,它應能區分毫伏量級的輸入信號差。如圖2中第二部分所示, M17,M18交叉互連實現正反饋,以提高比較電路的增益。

利用前級預放大器的輸出,控制鎖存器輸入電流I+,I_的變化,若I_遠大于I_,則M16和 M18導通,Vout-△0,Uout+=(2L16I+/WμnCox)+VTHN;

若I_增大而I+減小,M18的漏一源電壓升高,當高到M17的 VTHN時,M17導通,此時M17管開始抽取原來流過M16管的電流,這會使M16管的漏一源電壓下降,并導致M18管截止,電路的輸出狀態發生轉換。

當I-增大到一定程度時會導致M18進入飽和區,此時臨界電流值I-=(I+)(W17μnCox/L17)/(W16μnCox/L16),該電流臨界點也是輸出電壓發生轉換的臨界點。同理可得,當I+增大時,發生轉換的電流臨界點I+=(I-)(W17μnCox/L17)/ (W16μCox/L16)。

該鎖存比較器發生轉換時的輸入電壓差為1.37 mV。從鎖存器的瞬態特性可以看出,在輸入信號發生跳變時,通過比較輸入信號和2.5 V參考信號,鎖存比較器給出兩個向相反方向變化的輸出信號,實現了比較功能。

(2)輸出緩沖驅動級

輸出緩沖驅動級(又稱后放大器)的主要作用是把鎖存比較電路的輸出信號轉化成邏輯電平(0 V或5 V)。

如圖2中第三部分所示,M8,M10,M11,M13,M14,M15組成差分自偏置電路,它能吸人和供出較大的電流,使比較器在驅動大的容性負載時速度不受擺率的限制。

M9,M12組成一個反相器,用作附加的增益級,同時實現負載電容和自偏置差分放大器之間的隔離。要使輸出緩沖級工作在線性區,輸入信號的幅度一般要在1~3.5 V之間,所以在電路中串入M26管來提升鎖存器輸出電壓的幅值。

2.電路仿真

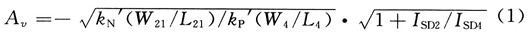

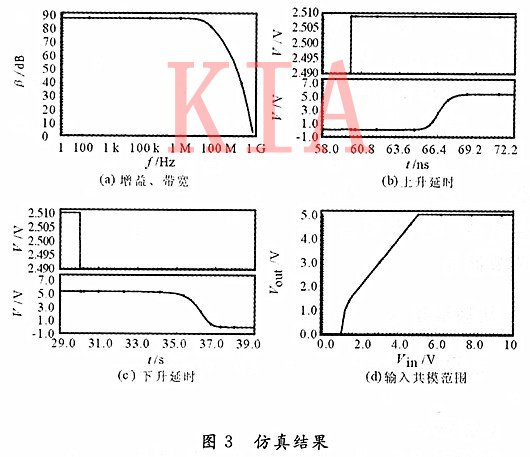

在5 V電源的電壓下,Vin-端加2.5 V參考信號,在Cadence軟件平臺下用Spec-tre工具對基于CSMC 0.5 μmCMOS工藝模型的電路進行仿真,得到比較器的增益、帶寬、上升延時、下降延時、輸入共模范圍如圖3所示。

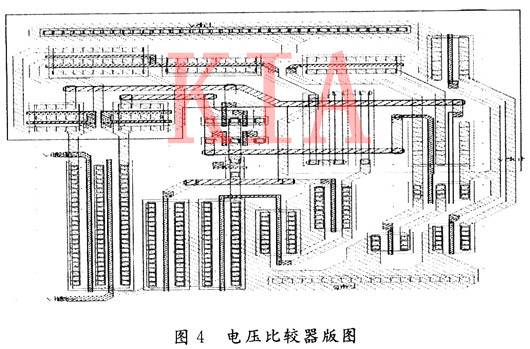

用Cadence自帶的Dracula工具對版圖進行驗證,通過設計規則檢查(DRC),該版圖符合CSMC0.5μmCMOS工藝的相關設計規則。

通過電路圖和版圖的對照(LVS),版圖中的器件及器件間的連接情況與電路圖中相一致,保證了該版圖是圖2所示電路圖的物理掩模圖形集。

此外,在做完DRC和 LVS后,版圖的電氣規則檢查(ERC)也同時完成了,這是Dracula工具的一個主要特點。ERC報告顯示該版圖中無短路、斷路等電氣規則錯誤。

3.版圖設計

集成電路的版圖是芯片在實際制作時物理掩模圖形的集合,是從電路原理圖到實際芯片的關鍵過渡環節。版圖的設計直接影響著芯片的最終性能。模擬集成電路版圖的設計要求更高,它不僅有技術成分,還需要許多藝術性的布局和走線。

基于CSMC 0.5μm CMOS(N-Well硅柵)工藝設計的集成電壓比較器版圖如圖4所示。

其中電阻為制作在N-well中的P+擴散條;MOS管為NORMAL器件,其溝道寬長為多晶硅柵覆蓋有源區部分的寬長。包圍有源區的N+diff和P+diff,用來表明管子是NMOS管,還是PMOS管,版圖面積為57μm×69 μm。

在CSMC O.5μm CMOS工藝條件下,采用預放大器、鎖存比較電路和輸出緩沖級級聯的鎖存比較電路結構,設計了一個高速、高精度的高性能集成電壓比較器,它具有低輸入失調電壓、低功耗的特點。

完成從電路原理圖設計到版圖設計和驗證(DRC,LVS)以及工藝角仿真和分析的整個設計流程。從仿真結果可以看出,這一高性能電壓比較器適用于高速A/D轉換器、高速數據傳輸器及高性能切換功率調節器等設備中。

聯系方式:鄒先生

聯系電話:0755-83888366-8022

手機:18123972950

QQ:2880195519

聯系地址:深圳市福田區車公廟天安數碼城天吉大廈CD座5C1

請搜微信公眾號:“KIA半導體”或掃一掃下圖“關注”官方微信公眾號

請“關注”官方微信公眾號:提供 MOS管 技術幫助